[ 🔍 CLICCA PER INGRANDIRE ]

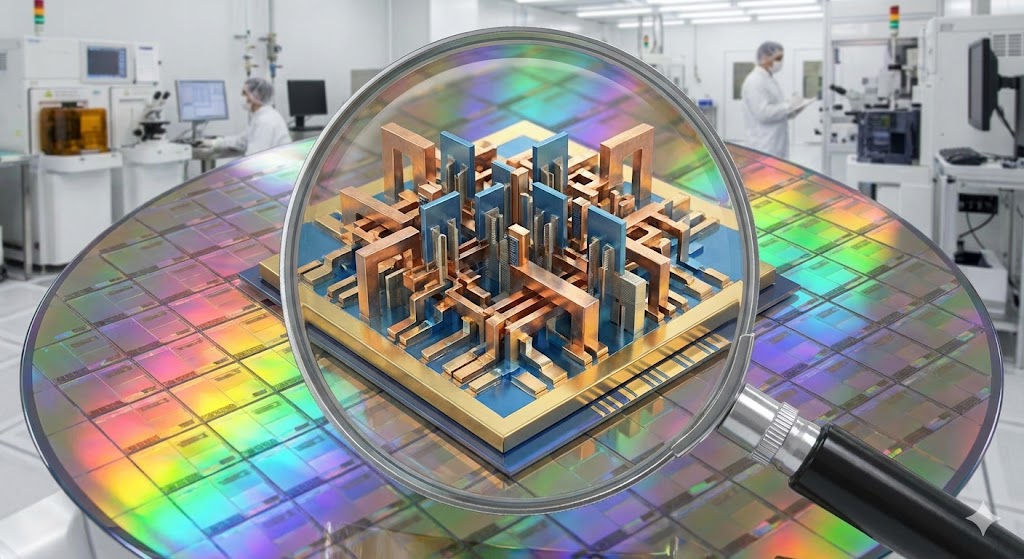

Rappresentazione visiva di un wafer di silicio con chip a 1 nanometro e ingrandimento microscopico della struttura dei transistor

L'industria dei semiconduttori sta per superare una barriera che fino a pochi anni fa sembrava impossibile: la produzione di massa di chip con processo produttivo a 1 nanometro. Questa nuova frontiera tecnologica promette prestazioni straordinarie e consumi energetici ridottissimi, ridefinendo completamente il futuro dell'elettronica.

La corsa verso l'infinitamente piccolo

La legge di Moore, formulata nel 1965 da Gordon Moore, co-fondatore di Intel, prevedeva che il numero di transistor su un chip sarebbe raddoppiato circa ogni due anni. Per decenni questa previsione si è rivelata straordinariamente accurata, guidando l'intera industria dei semiconduttori verso una miniaturizzazione sempre più spinta. Oggi, dopo aver raggiunto i 3 nanometri nel 2023 e i 2 nanometri nel 2024, l'industria si prepara al grande salto verso il processo a 1 nanometro, previsto per il 2027-2028.

Questa progressione non è soltanto una questione di numeri: ogni riduzione delle dimensioni dei transistor comporta benefici significativi in termini di prestazioni, efficienza energetica e densità di integrazione. Un chip a 1nm può contenere miliardi di transistor in più rispetto a uno a 3nm, garantendo potenze di calcolo esponenzialmente superiori in spazi sempre più ridotti.

Le sfide tecnologiche della produzione a 1 nanometro

Produrre chip a 1 nanometro rappresenta una sfida ingegneristica senza precedenti. A queste scale dimensionali, gli effetti quantistici diventano dominanti e i materiali tradizionali mostrano i loro limiti fisici. Il silicio, elemento fondamentale dell'elettronica moderna, inizia a perdere le sue proprietà isolanti quando le dimensioni scendono sotto i 2 nanometri, rendendo necessario l'utilizzo di nuovi materiali e architetture.

TSMC (Taiwan Semiconductor Manufacturing Company), leader mondiale nella produzione di chip, ha annunciato investimenti per oltre 32 miliardi di dollari nella ricerca e sviluppo del processo a 1nm. L'azienda taiwanese prevede di utilizzare transistor a gate-all-around (GAA) di nuova generazione, realizzati con nanofili o nanosheet di silicio, che offrono un controllo elettrostatico superiore rispetto ai tradizionali FinFET.

Samsung, altro gigante del settore, sta sperimentando l'utilizzo di materiali 2D come il grafene e il nitruro di boro esagonale (hBN) per sostituire parzialmente il silicio nelle regioni critiche del transistor. Questi materiali offrono proprietà elettriche superiori e permettono di superare alcune limitazioni fisiche del silicio alle dimensioni nanometriche.

L'importanza della litografia EUV avanzata

La chiave per produrre chip a 1 nanometro risiede nella litografia ultravioletta estrema (EUV) ad alta apertura numerica (High-NA EUV). ASML, unica azienda al mondo capace di produrre macchine litografiche EUV, ha sviluppato sistemi da 0,55 NA che permettono di "disegnare" pattern ancora più piccoli sui wafer di silicio.

Queste macchine, che costano oltre 400 milioni di dollari ciascuna e pesano circa 150 tonnellate, utilizzano luce con lunghezza d'onda di 13,5 nanometri per incidere circuiti microscopici sul silicio. La precisione richiesta è talmente elevata che l'intero sistema deve operare in condizioni di vuoto quasi assoluto per evitare che anche una singola molecola d'aria interferisca con il processo.

Intel, che per anni ha accumulato ritardi rispetto a TSMC e Samsung, ha ordinato diverse macchine High-NA EUV e prevede di recuperare terreno con il suo processo Intel 14A (equivalente a 1,4nm) entro il 2026, seguito dal processo Intel 10A (1nm) nel 2027.

Nuove architetture: GAA, CFET e transistor 3D

I transistor a 1 nanometro richiedono architetture radicalmente diverse da quelle tradizionali. I transistor GAA (Gate-All-Around), già utilizzati nei processi a 3nm e 2nm, verranno ulteriormente ottimizzati con la tecnologia MBCFET (Multi-Bridge-Channel FET), che utilizza nanosheet di silicio impilate verticalmente per massimizzare la densità di transistor.

Un'evoluzione ancora più avanzata è rappresentata dai transistor CFET (Complementary FET), dove i transistor NMOS e PMOS vengono impilati verticalmente uno sopra l'altro, riducendo ulteriormente l'ingombro laterale e permettendo densità di integrazione mai viste prima. Questa architettura potrebbe consentire di raggiungere densità superiori a 300 milioni di transistor per millimetro quadrato.

Alcune università e centri di ricerca stanno inoltre sperimentando transistor basati su nanotubi di carbonio e materiali bidimensionali come il disolfuro di molibdeno (MoS₂), che potrebbero offrire prestazioni superiori al silicio a queste scale dimensionali estreme.

Applicazioni e mercati dei chip a 1 nanometro

I primi chip a 1 nanometro saranno destinati alle applicazioni più avanzate e remunerative:

- Processori per smartphone premium: Apple, Qualcomm e MediaTek utilizzeranno chip a 1nm per i loro SoC di punta, garantendo prestazioni eccezionali con consumi energetici ridotti al minimo

- Data center e cloud computing: i server equipaggiati con CPU a 1nm offriranno capacità computazionali enormemente superiori, riducendo drasticamente i costi operativi dei grandi provider cloud

- Intelligenza artificiale: gli acceleratori AI a 1nm permetteranno di eseguire modelli linguistici di grandi dimensioni con latenze ridottissime e consumi energetici contenuti

- Automotive: i processori per veicoli autonomi richiederanno la massima potenza di calcolo nel minimo spazio possibile, rendendo i chip a 1nm ideali per questa applicazione

- High Performance Computing: i supercomputer del futuro utilizzeranno chip a 1nm per raggiungere l'obiettivo dell'exascale computing e oltre

I costi proibitivi e la concentrazione del mercato

La produzione di chip a 1 nanometro richiede investimenti colossali. La costruzione di una singola fabbrica (fab) in grado di produrre chip a questi nodi tecnologici costa oltre 20 miliardi di dollari, senza contare i costi di ricerca e sviluppo. Questo ha portato a una progressiva concentrazione del mercato: oggi solo TSMC, Samsung e, in prospettiva, Intel sono in grado di competere in questa fascia tecnologica.

I costi di progettazione di un singolo chip a 1nm sono stimati in oltre 1 miliardo di dollari, rendendo questa tecnologia accessibile solo ai più grandi player del settore come Apple, Nvidia, AMD, Qualcomm e poche altre aziende. Questa concentrazione solleva preoccupazioni sulla dipendenza tecnologica e sulla sicurezza delle forniture, specialmente considerando le tensioni geopolitiche tra USA, Cina e Taiwan.

Sostenibilità ambientale e consumo di risorse

La produzione di semiconduttori avanzati richiede enormi quantità di risorse. Una moderna fab consuma circa 10 milioni di litri d'acqua al giorno e richiede elettricità paragonabile a quella di una piccola città. TSMC ha annunciato ambiziosi piani per raggiungere la neutralità carbonica entro il 2050, investendo massicciamente in energie rinnovabili e sistemi di riciclo dell'acqua.

Paradossalmente, però, i chip più avanzati contribuiscono alla sostenibilità complessiva del settore tecnologico: un processore a 1nm può offrire prestazioni doppie rispetto a uno a 3nm consumando il 30-40% di energia in meno, riducendo l'impronta carbonica complessiva dei data center e dei dispositivi elettronici.

Il futuro oltre il nanometro: angstrom e sub-angstrom

L'industria dei semiconduttori non si fermerà al nodo a 1 nanometro. TSMC ha già annunciato piani per processi a 0,7nm e 0,5nm, denominati rispettivamente A7 e A5 (dove "A" sta per Angstrom, unità di misura pari a 0,1 nanometri). Questi processi ultra-avanzati potrebbero utilizzare architetture completamente nuove, come i transistor a tunnel a effetto quantistico (TFET) o addirittura tecnologie basate su spin electronics (spintronica).

Alcuni ricercatori stanno esplorando il computing molecolare e il computing quantistico come possibili successori della tecnologia CMOS tradizionale, anche se queste tecnologie sono ancora in fase estremamente sperimentale e la loro commercializzazione richiederà probabilmente decenni.

I semiconduttori a 1 nanometro rappresentano il culmine di decenni di innovazione continua e investimenti miliardari. Nonostante le immense sfide tecnologiche, economiche e ambientali, questa tecnologia ridefinirà le capacità computazionali dei dispositivi elettronici nei prossimi anni, aprendo possibilità che oggi possiamo solo immaginare. Il futuro dell'informatica si misura ormai in angstrom, spingendosi sempre più vicino ai limiti ultimi imposti dalle leggi della fisica quantistica.